# **ELFNET** Roadmap

# **European Electronics Interconnection**

Version 1

February 2007

### INTRODUCTION

Electronic interconnection technologies are in every sense key to global communication, security, safety and quality of life. The major systems and tools that modern society has come to rely on depend on transmission of electric current through joint interfaces.

These technologies are currently undergoing a global revolution with the implementation of new environmental technologies based on removal of hazardous substances from materials used in electronic and electrical equipment under the EU RoHS Directive and other similar legislation targeted for 2006-2010. Continued research and technology development will be vital to responding to this challenge.

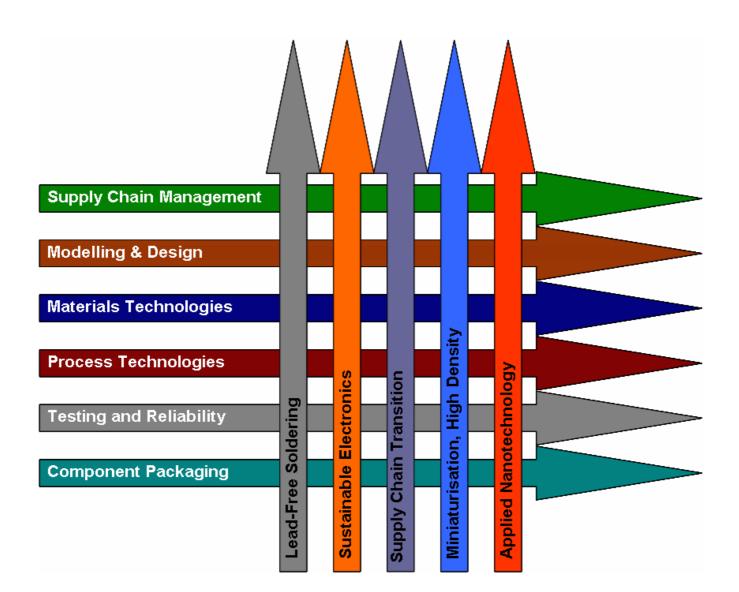

At the same time technology drivers are applying pressure to adapt interconnection materials technologies to ever smaller products with greater functionality and a more transparent and efficient life cycle. Some of these trends are quantified in Annex 1.

ELFNET, representing the critical mass of Europe's soldering technology experts, has been working during the transition to lead-free soldering to draw together this community in a series of meetings and web communications to define and resolve implementation issues.

Coherent collaboration in development and implementation of new technologies across European boundaries is the key to ensuring global competitiveness in the face of strong challenges from the US, Japan and the Far East.

This document represents a collective effort to look forward through and beyond the lead-free transition to technological development of electronic interconnection technologies generally. It complements the larger industry-standard documents such as the IPC, iNEMI and ITRS roadmaps, giving a particular perspective on cost-effective, sustainable and reliable technologies.

ELFNET (European Lead Free soldering NETwork) is a European network of national research organisations, technical experts and industry bodies enabling lead-free solutions in micro-electronics. It provides a platform to coordinate, integrate and optimise research, enabling electronic producers in the EU to optimise solutions and meet the EU deadline of introducing lead-free soldering in consumer products by July 2006.

ELFNET is supported by the European Commission and operates in 19 European countries. By facilitating 'best practice', ELFNET will continue to contribute to Europe's competitiveness in electronics manufacturing beyond 2006.

#### For more information contact:

Dr. Jeremy Pearce ELFNET Coordinator Soldertec Global Tel: +44 (0)1727 871311 info@europeanleadfree.net www.europeanleadfree.net

#### 1. Introduction

Environmental Supply Chain Management (ESCM) has been growing in importance over the last decade across industry sectors. However, only recently has it been driven by urgent legislative and market forces demanding more accountability and reporting on the environmental status of products.

This has been complicated by the trends towards complex, global, networked supply chains. Increasingly the OEM is further and further away from suppliers, both physically and in terms of data exchange. Even product design can now be the responsibility of the CEM.

The electronics industry is a classic example, with very significant increases in out-sourcing of work to CEM's and rapid advances in global procurement, exploiting important opportunities for economy in Central Europe, India and China, for example. Further, Europe has an industry that in some sectors is supported by countless SME's in 25 culturally diverse member states.

The introduction of the RoHS Directive in particular has massively increased the demand for ESCM, both in terms of the need to transfer data on hazardous substances and of the need to costeffectively source RoHS-compatible components.

Within this new paradigm there is an urgent need to collaborate in achieving harmonisation on information exchange protocols and formats, to avoid a chaotic multiplicity of practices and mountains of paperwork for those responsible for ESCM.

Whilst Japan and the US are largely achieving this, fragmentation and lack of communication has so far meant almost complete failure in Europe.

Looking forward over the next decade, it is inevitable that accepted practices will be developed by evolutionary default in the light of experience, particularly as enforcement regimes begin to have an impact. Further EU legislation, notably REACH, will add pressure shortly.

### 2. Materials Declaration

Declaration of materials used in supplied components has for some time been an established requirement for suppliers to some OEM's, notably within the automotive industry. Companies such as Ford and Sony use such mechanisms to proscribe and enforce their own environmental policies based on limitation or elimination of substances perceived as undesirable. New EU legislation such as RoHS and REACH are forcing the pace.

The first to address this issue significantly in relation to 'green electronics' was the Nordic GreenPack project 1999-2002. A <u>free web-based tool</u> was produced. The Danish RoHS Implementation Group also now publish <u>templates for declaration</u>.

In 2003/4 a global initiative involving EIA (US), EICTA (Europe) and JGPSSI (Japan) published the <u>Joint Industry Guide</u> (JIG), for generic use, covering what substances need to be reported and basic guidelines on data formats and applicability.

EIA/JEDEC worked with an industry drafting group, including some major European OEM's, to convert this to a standard JIG-101, published in May 2005.

The original JIG began a <u>major revision</u> process in September 2006.

In the meantime, JGPSSI in Japan produced a <u>'Survey Response' tool</u> and US industry groups delivered IPC standards <u>IPC 1752</u>, with a handbook<u>IPC</u> <u>1065</u>, both based on the JIG.

A number of other tools are being offered by industry on a more commercial basis, notably in the US. Examples include RosettaNet, GoodBye Chain Group and Omnify Software.

By contrast, the situation in Europe is still rather confused.

ZVEI, alongside EICTA a recognised European trade representative, produced a White Paper on the issue in October 2004 and held a special meeting on the topic in January 2006. This approach was hindered by a lack of clarity from the EU Commission on the precise definition of 'lead-free', with some false expectations amongst some during 2005 that it could refer to impurity levels of 0.1% of a 'unit', the unit being the whole component or even assembly. Thus generic 'Umbrella Specifications' and 'Flat Bill of Materials' were proposed, as used in other materials declaration contexts. It wasn't until August 2005 that the definition '0.1% of homogeneous material' was formally adopted, rendering these approaches inadequate.

The same issue affected drafting of a global standard. IEC TC3 published <u>IEC</u> 61906/DIN 19220 in June 2005. This also failed to 'drill down' to the level of 'homogenous material' required for RoHS compliance. The task to produce a refined standard was passed to IEC <u>TC 111 / HWG 2</u> but this has become bogged down in competing proposals from the US, France, Finland and even China.

Even now the debate is continuing on what exactly is required for compliance with RoHS. There is no regulation on the topic within the RoHS Directive itself. The current official <u>Commission FAQ</u> refers enquirers to the member state authorities who are 'currently discussing possible approaches'.

The UK's NWML has issued <u>guidelines</u> recommending Due Diligence including 'reasonable endeavours', but is the only member state to officially state this more low-key approach.

EICTA and ZVEI argued for a balanced approach, whereby full declarations are only required in cases where there is reason for concern. Further they were keen to utilise existing quality processes and supplier agreements to increase trust and minimise additional paperwork.

The best available information on what will be required is a non-legally binding <u>guidance document</u> published in May 2006 by the informal inter-governmental RoHS Enforcement Network, attempting to harmonise their enforcement approach.

This makes a distinction between larger companies whose entire product assurance systems will be probed and SME's for whom only product specific documentation will be required, including conformance certificates and RoHSelement materials declarations. All data is expected to be supported by evidence of data quality assessment procedures, including test analysis reports.

What is happening in practice today is hard to assess. Certainly most SME's at least would consider the costs of collating materials declarations for each component/product prohibitive and many are not actively looking at this option. Instead they are just using simple conformance certification (COC) documents covering the whole delivered package, often with wording agreed on a case-by-case basis with customers. Most simply use the BOM to go through the components, gathering whatever data is available from the various suppliers to verify compliance. Some may be unaware that this is not a 'materials declaration' as

such. Testing each homogeneous material is also thought unrealistic and testhouses are using an 'intelligent' experience-based approach to sample high-risk components. It has also been deduced that enforcement authorities will initially target a few larger, high-risk producers, allowing mainstream and smaller companies a significant time cushion.

Some OEM's are, however, insisting on materials declarations, notably in the automotive sector.

In fact it is very hard in law to define reasonable measures that a company should take in seeking to comply with such legislation and ultimately clarity can only truly come when test cases have been through the courts.

As a further issue, the actual data on substance content is often in fact not known or trustworthy.

Early efforts to survey suppliers for such data proved massively resource-intensive and singularly unsuccessful in eliciting response. Suppliers have also been slow to release such detailed information on component composition in product datasheets and/or the web. In this regard large component distributors, who sit in the middle of the supply chain, have played a very significant role in collating and publishing such data. Examples are <u>FarnellinOne</u>, and <u>PartMiner</u>.

The pressure to comply will inevitably lead to misrepresentation. Ultimately such data can only be verified by testing. However these protocols are not fully developed either.

The RoHS Enforcement Guidance document does partially address protocols for RoHS testing including sampling, following the generally accepted approach of XRF screening, with by more detailed tests as required. However, reference standards for relevant laboratory tests are still under development and a draft IEC standard from <u>TC 111 / WG3</u> on Test Methods is in draft but not yet released.

Surveying this situation and looking into the future it seems clear that in the shortterm there will exist a gap between currently stated theoretical compliance requirements and actual practice.

Companies are being forced by this paradigm shift towards implementation of a form of ESCM, though how this will involve materials declarations in not entirely clear. Given the considerable industry resistance and inexperience, coupled with a lack of clear guidance and leadership in Europe it could take maybe 5 years or more before industry practices are harmonised at an adequate level.

It is important to the competitiveness of the European market that variation in enforcement practices between member states is minimised. The continued work of the RoHS Enforcement Network will be important in clarifying what is required and this will need to be illustrated by test cases in court. National agencies need to do more to disseminate the available guidance, to SME's in particular, utilising available industry information agencies and networks.

European trade associations, by contrast with US and Japan, have not been able to

provide positive leadership and, once it is confirmed that materials declarations are indeed required, need to address this issue on behalf of the industry.

The IPC-1752 standard does exist, along with implementation tools and is being used by European companies. However the rigours of such a protocol are a strong deterrent.

The IEC standards process has shown a number of critical weaknesses, with delays, conflicting proposals and a lack of knowledge of what exactly is required. It is not clear today whether an IEC standard will ever be produced.

Technical and standards work on RoHS testing is underway by competent parties but needs completing with a high priority. Important developments in RoHS testing are expected in the next year.

In the longer term a technological solution can be foreseen whereby materials data is included in data sets exchanged within advanced supply chain IT communication systems. The demand for such systems is likely to grow as supply chains continue to become more complex and manufacturing becomes more virtual. For example, embedding of data in RFID tags within components could be envisaged.

There is, however, a large technology gap between such a system and today's PC/paper-based protocols, many using basic tools such as Microsoft Excel, Word and Adobe Acrobat. There is also an issue with the multiple IT platforms used, some highly customised and many very capital intensive. The <u>iNEMI Materials</u> <u>Composition Data Exchange project</u>, associated with the development of IPC 1752, made significant advances in moving towards universal data exchange

formats.

## 3. Marking & Labelling

### Lead-Free Labelling

It was assumed in the early development stages of lead-free soldering that some form of labelling would be used to denote products and components that were leadfree soldered. In practice this has proved a more complex challenge.

The initial focus was on a 'lead-free' symbol – for example a leaf or crossed Pb symbol. Panasonic used a leaf symbol on their Minidisc player when it was released in 1999. European contributions to this field came from Soldertec and from the EFSOT project.

Multiple variations of such symbols began to propagate and the debate broadened as industry began looking for a 'RoHScompliant' label rather than just 'lead-free'. Over time it was perceived that the purpose of many such symbols was mainly marketing, although they are useful on packaging for customs and inventory control. Both the IPC and IEC refused to consider a compliancy-based standard.

Compliance markings have however developed through various quality assurance agencies, as a part of their normal operations. Examples are the <u>BSI</u> <u>'RoHS-Trusted Kitemark</u>' and the TUV <u>'RoHS Mark'</u>.

Technical efforts have since focussed more on using a marking to convey useful technical materials information to assist with compatibility issues in assembly and upstream work such as rework, repair and recycling.

In 2004 JEDEC published JESD97 and IPC published a new version of IPC-1066.

These have now been combined and will be republished as J-STD 609 shortly.

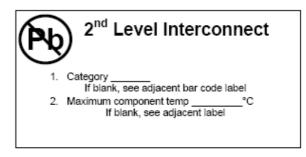

These standards focus on 2<sup>nd</sup> Level Interconnects, defined as the connection made be attaching a component to a circuit board. They provide labels for components with simple crossed-Pb symbol, Category and Maximum components temperature.

J-STD 609 Component label

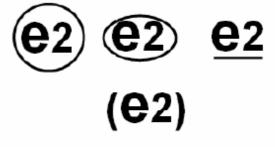

Categories define the material/terminal finish, for example 'e2' is SAC alloy.

Board level markings are also included in

J-STD 609 Material category label examples

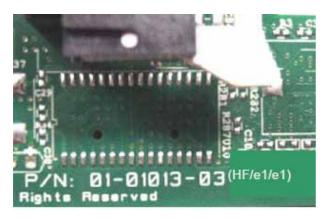

the J-STD 609 standard, with a standardised code sequence. This includes 'HF' (Halogen-Free), 'eX' codes for solder and finish, 'bX' codes for board finish and 2 letter 'XX' codes for conformal coating.

J-STD Board marking example

One weakness of this approach is that some components are far too small for any kind of marking. There are obvious problems with bare die, for example. In this case the marking can only be used on the lowest level shipping container.

In 2004 the Japanese produced a Guidance Document ETR-7021 and a report on semiconductor marking EIAJ EDR-7605. These showed some disharmony with the US approach. For example more detailed coding is used to describe the exact solder alloy composition used. 'A30C5' for example, denotes Sn3Ag0.5Cu alloy. In July 2005 a Guidance Document ET-7001 was published.

Finally a Japanese standard JIS C 950 was published in December 2005. This covered all RoHS elements and introduced new symbols:

Japan JIS C 950 markings

These labels are used in conjunction with whole product labels describing the

various sub-parts of equipment – speakers, cabinet, CRT etc – and stating whether or not RoHS elements are present in each.

These same symbols, but with different content are also being used in China in a standard currently being drafted.

These markings have a particular significance, because, unlike the RoHS Directive, they will form a part of the legal enforcement of substance bans in Japan and China.

As for a global standard, the IEC TC97 stalled in December 2005 over competing proposals and questions over the feasibility and use of a unified label. It has been decided that instead a Technical Specification will be published, initially based on a Japanese proposal.

Apart from the Japanese approach, current concepts for marking are not comprehensive enough to deal with the total supply chain, recycling, repair, endof-life treatment etc. Neither do they include information on complexities such as RoHS exemption.

To summarise, the debate over different markings appears to be resolving into identifiably different types of marking.

- Customised packaging-based labels for marketing, customs and inventory control

- Product-based RoHS compliance markings issued by recognised quality agencies

- Product-based RoHS substance declarations by sub-part

- Component and Board-based technical markings

US standardisation processes have focussed on the latter type, for lead-free and halogen-free only, and this has been

followed by those Europeans who are using technical markings. The Japanese and Chinese approaches have additional product-based substance markings and are broader, covering all RoHS elements. The IEC contribution remains to be seen. Other label types are industry driven only.

From a European perspective there is no rationale or available agency to begin any new independent initiatives. In practice the J-STD 609 will probably be adopted for technical marking. Customised product and packaging-based labels are likely to continue in the short-term.

It is probably not too late for an authoritative industry-based European forum to consider the status of marking & labelling and provide clear guidance on appropriate action for companies. Enough information and clarity now exists to enable reasonable forecasting and planning. Such a forum could also collate industry feedback and respond to the request of IEC TC91 committee for input to the proposed Technical Specification.

In the medium-term, once the RoHS transition is complete, perhaps by 2010, the incentive for labelling in general is likely to diminish, since the majority of goods will be RoHS compliant.

In fact it is probable that the focus of attention will turn to labelling noncompliant products, particularly for sectors such as aerospace and defence where obsolescence is a significant issue.

Recycling will grow in importance and requirements, such as those already in the WEEE Directive, to label goods with the presence of hazardous substances may become a major issue. In this case the Japanese substance-declaration approach is most relevant. Technical markings are likely to persist as their information will continue to be relevant in assembly and repair/rework. It remains to be seen whether new lead-free materials will proliferate or whether the industry aim to move towards single solutions will be achieved. This will to some extent determine the long-term future of this type of marking.

As for Materials Declaration, there could be significant technology advances over the next decade beyond the current paper/package-based labelling systems towards advanced IT-based solutions carrying a larger data set in a more comprehensive, readable and transferable form.

2D bar-coding is an intermediate technology step, but this relies on universal use of barcode reader technologies and, ideally integration with existing inventory systems.

### **Component Numbering**

Whether or not to renumber components as lead-free/RoHS compliant has been a significant debate in practice.

Whilst it may seem logical in regard to the ability to inventory control and separation of complaint and non-compliant components, many component suppliers were reluctant to do so.

Part of the issue relates to how long the RoHS transition is expected to be. In theory, if it is reasonably short then a great deal of extra investment would be required to, for example, add a prefix to each component even though this would become redundant once all components were RoHS-compatible. In fact the situation would the reverse since it would then be necessary to identify the minority of non-compliant products.

Philips, who didn't change numbering, argued that doing so would unnecessarily increase customer's costs in BOM revisions and doubling of inventory control systems. In any case, for the majority of components there were no compatibility issues. In fact many shipped components, passives in particular, were already leadfree for some time without the customer realising.

The majority of users, however, gave very strong positive reactions to surveys in the US demanding that part numbers were changed. The NEDA RoHS Summit in January 2006, for example, concluded with <u>a statement</u> demanding new numbers.

With new part numbers it is more obvious when the transition had been made for each component, instead of relying on individual date-based change information. This enables segregation and reduces the risk of cross-contaminations. The case is particularly strong for BGA's where there is a higher risk of compatibility problems and very significant cost of failure should a lead-free product be used unknowingly in a SnPb process. The aerospace/defence industries have particular needs, including the simplest possible way to track non-RoHS components for obsolescence processes.

In response, some component distributors chose to renumber parts themselves. <u>FarnellInOne</u> is an example. Another distributor, <u>Arrow</u>, launched an online database of suppliers marking and numbering policies.

For some companies, relocating incoming parts and product designs into a fullysegregated system, the renumbering issue becomes largely irrelevant.

There have been calls for standardisation of practice regarding the new numbering

systems used, since there are currently a myriad of different coding systems used by suppliers. However in practice this appears to be rather too late and unrealistic.

Component renumbering example

Thus all has probably been said and done that could be on this issue. The status quo is clearly non-ideal, but hasn't yet been an obstacle to implementation.

As RoHS implementation proceeds during the next decade, systems will continue to adapt as at present. Renumbered components will probably remain so, otherwise disruption will duplicate in the reverse sense. Identification of noncompliant components will become more important for exempted industries such as aerospace/defence.

### 4. RoHS Component Availability

Availability of RoHS compatible components has always been a high priority concern for the industry. In the early years of the development there was a strong impression that the components suppliers were not responding and indeed, some research work was hindered by lack of components.

However, major suppliers appear to have largely met the July 2006 deadline for relevant product sectors at least. Passive components have in fact been available for some time.

Major component distributors have seen competitive advantage in making available RoHS information, component databases and products and provided a strong link in the supply chain as a result.

Still, there are thermal stability issues with some actives, notably those that are particularly temperature sensitive. Examples are tantalum caps and LED's.

Of major concern to currently exempted sectors is the continued supply of noncompliant SnPb components. These will be required by, for example the aerospace/defence sector for many years to come – not just for manufacture but also to deal with obsolescence. Major procurement operations for SnPb components have been underway for some time.

There is reason for some concern over the continued supply of some SnPb products, with reports that some suppliers will axe up to 1/3 of their inventory due to non-profitability. Over time it is predicted that the cost of SnPb components may rise as supplies become restricted.

It is now clear, however, that dual supply of SnPb and Pb-free products may be needed for some time. SnPb BGA's will be especially required since lead-free products are less compatible with SnPb processes. The lead-free transition period is likely to extend to 2010 and beyond. For example recent recommendations regarding Category 8&9 products have referred to 2016 as a target date for some equipment.

During the transition there is enormous cost pressure for smaller suppliers who failed to clear inventories in time to pass off components as RoHS compatible. Already a grey market has appeared and counterfeiting has been detected. This is a short-term issue.

Recently a new RoHS exemption has been approved for lead in finishes of 'fine-pitch' components, over concerns related to tin whiskers. It may be however that this has come too late to effectively reverse transition to lead-free finishes for such components.

Future work will be needed to complete the development of compatible components, particularly materials technologies for thermally challenged products.

Exempted sectors are already considering supply and obsolescence issues strong enough drivers to make the lead-free transition without direct legislation. However these sectors are generally also concerned about reliability and this will need to be addressed.

| High Priority                     |                                               |                                                                                                                                                                                       |                                                                                                             |        |

|-----------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------|

| Issue                             | Challenges                                    | R&D Needed                                                                                                                                                                            | Notes                                                                                                       | Target |

| Materials<br>Declaration          | More clarity on what is required              | Study of industry practices                                                                                                                                                           | Review ZVEI, IPC, JEITA proposals                                                                           | 2010   |

|                                   |                                               | Clear, harmonised industry-<br>led guidance with<br>government support                                                                                                                | Link to EU RoHS<br>Enforcement<br>Network                                                                   | 2010   |

|                                   | New tools for<br>materials data<br>handling   | International standard on<br>materials declaration<br>templates and data formats                                                                                                      | IEC standard<br>required – target<br>50% use by 2010                                                        | 2010   |

|                                   |                                               | New concepts for multiple<br>degrees, levels of declaration<br>with direct relation to RoHS,<br>REACH etc compliance                                                                  | Refer IPC 1752,<br>1065                                                                                     | 2010   |

| Marking &<br>Labelling            | Industry<br>harmonisation                     | Study of industry practices                                                                                                                                                           | Assess use of IPC<br>standards, J-STD-<br>609                                                               | 2010   |

|                                   | Clearer standards                             | Better definition for<br>IPC\JEDEC e1-e9<br>classification, especially e3-<br>tin                                                                                                     | Use e0 for SnPb                                                                                             | 2010   |

| RoHS<br>Component<br>Availability | Thermally<br>compatible<br>components         | New materials, designs for<br>mitigation of thermal damage<br>to components, laminates                                                                                                | Industry to develop guidelines                                                                              | 2010   |

|                                   | Shelf-life data for<br>new components         | Comprehensive review of<br>shelf-life issues for lead-free<br>components and laminates<br>including solderability, MSL,<br>processability                                             | Work with <u>COG</u><br>forum. Propose IEC<br>TC91/WG10<br>delamination<br>guideline, towards<br>a standard | 2010   |

|                                   | Continued<br>availability of SnPb<br>products | Formation of RoHS-<br>exempted industry groups to<br>consider measures relevant<br>to SnPb supply –<br>obsolescence, labelling,<br>mixed assembly, lead<br>contamination, reliability | Work with COG<br>Forum.                                                                                     | 2010   |

|                                   | Medium Priority              |                                                                                   |                                                                 |        |  |  |

|-----------------------------------|------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------|--------|--|--|

| Issue                             | Challenges                   | R&D Needed                                                                        | Notes                                                           | Target |  |  |

| Marking &<br>Labelling            | Industry<br>harmonisation    | Industry-led guidance                                                             | Review and<br>combine IEC, IPC,<br>JEITA. Input to IEC<br>TC91. | 2015   |  |  |

|                                   | More efficient data transfer | UV labelling on fully<br>compliant components                                     |                                                                 | 2015   |  |  |

| RoHS<br>Component<br>Availability | Better RoHS<br>Testing       | European standardisation of equipment, protocols and calibration for RoHS testing | IEC standard in<br>development<br>(delayed)                     | 2015   |  |  |

|                                   |                              | New standards, reference<br>materials for XRF testing                             |                                                                 | 2010   |  |  |

|                                   |                              | Certification by independent,<br>accredited European<br>agencies                  |                                                                 | 2015   |  |  |

| Low Priority                      |                                       |                                                                                   |       |        |  |

|-----------------------------------|---------------------------------------|-----------------------------------------------------------------------------------|-------|--------|--|

| Issue                             | Challenges                            | R&D Needed                                                                        | Notes | Target |  |

| Marking &<br>Labelling            | More efficient data<br>transfer       | New product tagging and<br>data tools based on RFID-<br>type technology           |       | 2020   |  |

|                                   |                                       | New cross-platform tools and protocols for data exchange                          |       | 2020   |  |

| RoHS<br>Component<br>Availability | Thermally<br>compatible<br>components | More thermally efficient soldering process equipment, reducing excess temperature |       | 2020   |  |

#### 1. Introduction

With the increasing complexity of the modern world there is a generic demand for more modelling and simulation to be used to characterise systems and provide design input, as well as for new design tools. These are required to optimise systems management and reduce costs.

In the case of electronics interconnection this has a strong relevance in a number of ways.

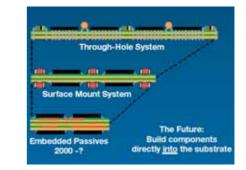

Electronic designs are rapidly becoming smaller with higher interconnection densities and increase in component mix. Design tools and design rules will need to be evolved to better deal with emerging technologies such as embedded systems, 3D interconnects, 3D-MID and mixed mode wireless.

Indeed, there are few if any tools relevant to impending developments in nanoscale, chemical, biological and opto-electronics.

Within mainstream design, new objectives are proliferating to meet demands for optimisation of reliability, manufacturability and environmental compatibility, for example. All of these issues have been recently prioritised by the introduction of lead-free soldering, coupled with significant changes to the electronics supply chain structures.

Lead-free solders with a diversity of sometimes complex microstructures are replacing 'standard' SnPb solders. Basic materials data is only just now being compiled to feed solder joint modelling tools, though new models for reliability are only in their infancy.

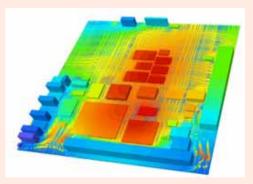

Thermal issues have become dominant, especially in lead-free solder processing of large and complex boards, with experience of warping, delamination and other effects. New work on modelling is underway to characterise heat and stress distribution, optimising design and mitigating process problems.

Modelling will be used increasingly for simulation of supply chain management, assembly and test procedures.

## 2. Stress Modelling

Modelling of stress in electronics assemblies and solder joints is an advanced science, using FMEA and other techniques, benefiting from recent improvements in data handling and computation speeds. It is used in design and also to predict product lifetimes.

Europe has many research centres specialised in this area from universities, RTD's and large companies. A sample can be seen in the list of <u>organisers of the</u> <u>EuroSIME group</u>. This group has held annual conferences on thermal, mechanical and multiphysics simulation for a number of years.

The scope of this topic is potentially broad and could include semiconductor packaging, MEMS, flexible circuits and conductive adhesives for example.

The proliferation of new devices and new forms, such as embedded devices will need to be handled by the modelling tools of the future.

However, a focus on lead-free solder joints is the most generic, high impact and urgent approach. The key driver is a link to reliability, where large sectors of the currently RoHS-exempt sectors have concerns. ELFNET has established an expert group for lead-free solder joint reliability whose work could include specific activity on modelling.

However, the impact of lead-free soldering has been so great that an already complex science has required radical rethinking. With regard to lifetime prediction, for example, models for longterm reliability (> 5 years) were not even available for SnPb joints. Now, for leadfree solders, lifetime prediction is "at zero". The problem is centred on the complexity of the new solder materials. We are moving from a largely simple, single SnPb material to several multielement material solutions, with complex microstructures, new properties and new failure modes. Whilst the basic joint geometry remains the same, the materials properties need understanding before models can work. This could take years.

ELFNET has worked with the COST 531 initiative to take a first step in this direction by publishing <u>a comprehensive database</u> of lead-free solder alloy properties, initially listing 32 SAC alloy family members. This is being expanded to other alloy families.

The fundamental micro-nano structural basis for this data is still being explored, with new data on brittle-ductile behaviours, interface morphologies and creep still being produced. What is already known is that much of this is non-linear and inhomogeneous, questioning viability of modelling at this level.

Further, there is a realisation that leadfree solder joint properties can be a function not just of the material but of the component geometry and substrate warpage, for example. This could lead to an alternative and more empirical approach, using a more holistic model of the electronic assembly, with greater consideration of the mission profile and more linkage to real-life field data.

## 3. Thermal Simulation

### **Process Modelling**

Thermal issues in solder processing have become much more important now that the increased temperatures and narrower process windows of lead-free soldering have to be considered.

This was initially driven by concern over temperature sensitive components particularly, but more recently by issues related to substrate damage for larger and more complex boards.

Here it was realised that problems were not solely a function of solder, component or substrate materials, but also of assembly design. Positioning of larger heat-absorbing components and via density for example can be aggravating factors. Thus a holistic approach may be able to give the most valuable data.

Here, good modelling is clearly desirable as a cost-effective alternative to the trialand-error approach.

Several new developments are currently in progress aimed at adaptation of traditional software such as <u>Flowtherm</u> for use in process modelling. It is expected that there will be more advances in this area.

Whilst most of the focus may be on mass soldering techniques, and reflow soldering in particular, there is also application to manual soldering, and rework/repair processes in particular, where some severe thermal issues have been observed in some cases.

### **Joint Modelling**

Thermal modelling of electronic interconnections has a number of relevancies and is likely to become more important as the complexity of electronics interconnection technologies increase.

Much work has been done and will continue to be done to study the solidification processes in solder joint formation, particularly in relation to microstructure development. An example is the <u>MICRESS software</u>.

Work is in progress by Prof. Muller at TU Berlin and Prof. Geers at TU Eindhoven.

Modelling is also being applied to development of new soldering techniques such as laser soldering to study localised heat dissipation.

Similar technology is applied along with stress modelling to simulate joint reliability, including thermal cycling tests.

Thermal simulation will become more important for nanoelectronic or embedded interconnections where thermal effects may be important but where tools for practical measurement of such effects are constrained by size or access limitations.

## 4. Design Tools & Methodologies

The proliferation of new electronic interconnection technologies, both at the PCB and component packaging level, will continue to challenge design tools and methodologies. At the same time, design and the integration of design with assembly processes is likely to become more important in cost-effective systems management.

Adaptation to the new technologies is likely to require very significant investment in tools that are already considered expensive.

There is now a whole family of terms pointing to the growing importance of design including Eco-Design, Design for Environment (DfE), Design for Manufacture (DfM) and Design for Reliability (DfR) for example.

DfM is concerned with creating new ways of optimising the manufacturing operation by, for example thinking more carefully about test access points and equipment limitations. Breakthroughs will come from better business integration between the design and manufacturing functions, often dislocated both geographically and culturally by OEM outsourcing.

In the case of radically new technologies such as lead-free soldering it can be the design function that lags behind and this needs to be addressed by personnel training, better cooperation with experts and a stronger sense of responsibility for the whole product manufacture.

Technology advances will include better tools and algorithms for multi-platform, multi-site data transfer. Assembly feedback systems will improve efficiency. DfR will become very important for socalled high-reliability applications in harsh environments – automotive, aerospace and defence, for example. However, for lead-free soldering and also other new technologies, the basic principles of reliability and joint failure are as yet missing basic understanding and necessary parameters.

An example of the linking of design with reliability in the field of lead-free soldering is the work of the <u>iNEMI High Reliability</u> <u>Task Force</u>, who are issuing guidelines, including materials selection, for mitigation of tin whisker risk.

### 5. Standards & Design Rules

Collaborative processes for producing standards and design rules typically suffer from a lack of engagement under normal circumstances but then lack the speed and representation demanded when revolutions such as lead-free soldering are introduced.

Inevitably, especially in a fragmented Europe, there can be a lack of leadership, harmonisation and even technical knowledge. In some specific examples for lead-free standards there have been significant difficulties in achieving global harmonisation. US IPC\JEDEC processes have arguably achieved faster and higher profile progress. Japanese developments have been important but lacking in communication.

Completion of standards revision for leadfree soldering is thus likely to take several years.

Several projects focused on European SME's in particular have produced design and/or workmanship guidelines for leadfree soldering. The first was probably the Scandinavian <u>NoNE</u> project. More recently the EU projects <u>GREENROSE</u>, <u>LEADOUT</u> and <u>LFS-for-SME's</u> have attempted to provide such tools.

There are some specific requirements for harmonisation, in connector designs for example. The wide variety in lead-free finishes has led to some calls for better harmonisation and/or movement towards a single solution.

There are also broader needs for improvement of the basic standards protocols themselves. As technologies become more diverse generic standards may need to be developed into more precise and more sector-specific documents.

| High Priority                   |                                               |                                                                                                                               |                                                                                   |        |

|---------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------|

| Issue                           | Challenges                                    | R&D Needed                                                                                                                    | Notes                                                                             | Target |

| Stress<br>Modelling             | Better collaboration                          | European expert group                                                                                                         | ELFNET reliability network                                                        | 2010   |

|                                 | Knowledge of<br>interconnection<br>properties | Lead-free solder alloy<br>properties database                                                                                 | Extend<br><u>ELFNET/COST 531</u><br><u>database</u> . See also<br><u>SURDAT</u> . | 2010   |

|                                 |                                               | Tools for modelling of solder<br>alloy microstructure evolution<br>and ageing                                                 | Some work in<br>progress                                                          | 2010   |

|                                 |                                               | Effect of solder creep -<br>interaction with stress,<br>material behaviour –<br>cracking, stress relaxation                   | Needs connection with failure                                                     | 2010   |

|                                 |                                               | Collation and analysis of<br>real-life field data for solder<br>joint behaviour.                                              | Company-specific<br>infrastructure to<br>collect non-public<br>information        | 2010   |

|                                 | New tools and methodologies                   | Categorisation of stress missions                                                                                             | Very product<br>specific, but<br>material suppliers<br>need defined<br>standards  | 2010   |

| Design Tools &<br>Methodologies | Design for<br>Reliability (DfR)               | New tools and protocols for<br>high reliability products                                                                      | Modelling, failure modes                                                          | 2010   |

|                                 |                                               | Inclusion of statistical algorithms                                                                                           | Mathematical<br>models to be<br>converted to<br>statistical software<br>packages  | 2010   |

| Standards &<br>Design Rules     | More harmonisation                            | Lead-free finishes                                                                                                            |                                                                                   | 2010   |

|                                 | Adaptation to new technologies                | New pad designs foe lead-<br>free technology                                                                                  |                                                                                   | 2010   |

|                                 | Better standards                              | More precise specifications with more pass/fail criteria                                                                      |                                                                                   | 2010   |

|                                 |                                               | Sector-relevant approach -<br>high temperature, high<br>reliability, harsh environment,<br>consumer, military etc<br>products | Product-specific<br>tests ideal                                                   | 2010   |

|                                 |                                               | Medium Priority                                                                                                            |                         |        |

|---------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------|--------|

| Issue                           | Challenges                                    | R&D Needed                                                                                                                 | Notes                   | Target |

| Stress<br>Modelling             | Knowledge of<br>interconnection<br>properties | Modelling tools for alloy<br>thermo-physical and<br>mechanical property<br>prediction                                      |                         | 2015   |

|                                 |                                               | Use of quantum mechanics,<br>atomic level R&D, to better<br>understand nanoscale<br>complexities of<br>interconnections    |                         | 2020   |

|                                 | New tools and methodologies                   | New tools for measuring stress/strain in warpage for acceptance criteria                                                   |                         | 2015   |

|                                 |                                               | Non-linear models for new failure modes e.g. brittle, IMC, interface reactions for acceptance criteria                     |                         | 2015   |

|                                 |                                               | Use of statistics in structural<br>analysis for Design Rules to<br>analyse maximum dispersion<br>of dimensional parameters | Limits dispersions      | 2015   |

| Design Tools &<br>Methodologies | Cost                                          | More cost-effective design<br>tools, and methodologies e.g.<br>direct data transfer to<br>assembly                         |                         | 2015   |

| Standards &<br>Design Rules     | More harmonisation                            | Land patterns within package diversity                                                                                     |                         | 2015   |

|                                 | Adaptation to new technologies                | Complete revision of<br>European standards for<br>implementation of<br>RoHS/lead-free technologies.                        |                         | 2015   |

|                                 |                                               | Emerging technologies e.g.<br>embedded devices, 3D<br>interconnection, 3D-MID,<br>plastic electronics                      |                         | 2015   |

|                                 |                                               | Better board sub-panelisation for smaller form factors                                                                     |                         | 2015   |

|                                 |                                               | Shear-pull tests                                                                                                           |                         | 2015   |

|                                 |                                               | Warpage measurements                                                                                                       | Real-world verification | 2010   |

|                                 |                                               | Microvia definitions                                                                                                       |                         | 2010   |

|                                 |                                                   | Low Priority                                                                                                              |       |        |

|---------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------|--------|

| Issue                           | Challenges                                        | R&D Needed                                                                                                                | Notes | Target |

| Stress<br>Modelling             | Knowledge of<br>interconnection<br>properties     | Use of quantum mechanics,<br>atomic level R&D, to better<br>understand nanoscale<br>complexities of<br>interconnections   |       | 2020   |

|                                 |                                                   | Fundamental materials data<br>for nanoscale and biological<br>interconnections                                            |       | 2020   |

|                                 | New tools and methodologies                       | Holistic FMEA approach<br>integrating influence of<br>materials, process,<br>degradation etc                              |       | 2020   |

|                                 |                                                   | Atomic level models for<br>predictive failure on<br>nanoscale                                                             |       | 2020   |

| Thermal<br>Simulation           | Adaptation of FEM<br>tools to new<br>technologies | New tools for holistic thermal<br>simulation at product, board,<br>component and joint levels in<br>both process and use. |       | 2020   |

|                                 |                                                   | Scaling of models from board level towards nanoscale interconnection                                                      |       | 2020   |

|                                 |                                                   | Parameters for new materials, including intermetallics                                                                    |       | 2020   |

| Design Tools &<br>Methodologies | Adaptation of tools to new technologies           | Improved tools for emerging technologies e.g. embedded passives, optoelectronics                                          |       | 2020   |

|                                 |                                                   | Integrated tools for mixed-<br>mode wireless                                                                              |       | 2020   |

|                                 |                                                   | New tools for high density designs                                                                                        |       | 2020   |

|                                 | Cost                                              | Simulation of assembly line<br>performance, supply chain<br>management, QC tests for<br>optimum ROI                       |       | 2020   |

|                                 | Better design for<br>manufacturing<br>(DfM)       | Identification of factors, generation of metrics                                                                          |       | 2020   |

|                                 |                                                   | Inclusion of test access in design                                                                                        |       | 2020   |

|                                 |                                                   | New multi-platform, multi-site data transfer protocols.                                                                   |       | 2020   |

|                                 |                                                   | Improved DfM algorithms for CAD                                                                                           |       | 2020   |

|                                 |                                                   | Better systems integration<br>e.g. assembly data feedback,<br>OEM in-house DfM                                            |       | 2020   |

#### 1. Introduction

Never before has the electronics industry faced so many radical changes in the basic materials used for its assemblies. Compatibility issues mean that the advent of lead-free soldering is not only changing the basic solder alloy but also component and board finishes, boards and component packaging materials. Further, the impact of halogen-free legislation has not yet been fully realised.

Work on alternative lead-free solder alloys has been underway since the 1980s and it has taken many years since to study interactions with metal finishes on components and boards and develop new solutions. This work continues and is likely to do so for the foreseeable future.

Research continues to build and refine solder alloy compositions based on the basic SAC alloy family and widen the scope to include low temperature and high reliability solutions. At the same time, the recent industry experience of the high costs and reliability risks of qualifying new solders is pressuring against new variations and towards single solutions.

There is still no viable cost-effective alternative to high-lead high temperature solders used in component packaging. Work on conductive adhesive technology as a replacement for soldering altogether continues but faces significant challenges.

Other assembly materials such as underfills, encapsulants and inks are also being adapted to the new processing environment. Conformal coating technology needs some new thinking.

Substrate technology is not in general dealing well with the twin challenges of higher processing temperatures for lead-free soldering and the need for halogen-free solutions. This needs urgent attention.

Work needs to be done to develop materials with better CTE matching to mitigate current thermal issues in both processing and use.

### 2. Lead-Free Solders

#### SnAgCu Solders

The SnAgCu, or SAC, alloy family, with its reduced form SnCu, has become the alloy of choice for the majority of the European market. This recommendation was made by both <u>Soldertec</u> and <u>iNEMI</u> in 2000, following results of earlier projects, notably the <u>IDEALS project</u> in Europe.

They had already been applied in the automotive industry for under-bonnet applications due to their improved robustness over SnPb.

There has been a plethora of formulation variations with the SAC alloy family, with 33 being chronicled in ELFNET/COST 531 database. This has been largely due to patenting and commercial issues. The IPC Solder Products Value Council recently studied the effect of this variation in a large collaborative program and concluded that there was very little performance difference between commonly used formulations.

Low-silver alloys have nevertheless been an important new development, mainly aiming at reducing costs of Ag. Work has included the <u>discovery that SAC101</u> has benefits for use in BGA solder ball adhesion and shock resistance in mobile devices.

More significant variation is likely to arise from practical effects such as differences in solder alloy paste properties. Most of Europe's major solder manufacturers have been key players in lead-free soldering research since its beginning in around 1990. They have been able to refine solder ball production, size distribution, flux chemistry and paste rheology, for example. A large number of smaller suppliers have needed to catch up with this proprietary knowledge. Thus there have been very wide variations in paste performance for nominally the same alloy formulation and this is likely to continue throughout the lead-free transition.

Solder pastes have been adapted for specialised use, for example tombstoning prevention and voiding control. It is likely that suppliers will continue to compete for differentiation in this way for some time and that paste and flux technologies will evolve over the next few years.

SAC+ variants began to appear quite early in the transition, the most well-known being the Nihon Superior 'Ni-stabilised' product, claiming improved wettability and finish, notably for SnCuNi in wave soldering.

Early projects explored the effects of the additional elements of SAC alloy properties, in particular amongst the automotive community who were seeking to strengthen the alloy. An example was the <u>INNOLOT project</u>. These effects are now reasonably well-known and some results <u>were presented</u> within ELFNET.

SAC alloys with Ni, Co, Mn and Ge are now also used as ball materials for arrays.

However, whilst the effects of these additions on microstructure are known to some degree, the links between microstructure and reliability are only now being explored. Thus this, along with the concept of adding nanoparticles in socalled 'composite solders' can still only be largely empirical.

Nevertheless, with the strong pressure for high-reliability applications to conform to lead-free solutions projects such as the <u>GEAMCOSS</u> and <u>AMELIE</u> projects aimed at 'high-reliability solders' are likely to multiply and will contribute well to the basic science.

#### Low Temperature Solders

A major reasoning for introduction of SAC alloy was the tolerance of lead in a transitional period. It was envisaged that second generation alloys, potentially cheaper and lower temperature processing, would later be introduced.

There is also a desire to use lower temperatures to avoid thermal problems from lead-free processing and also to reduce energy consumption.

Much research has already been carried out on SnZn, SnBi, SnZnBi alloys and their myriad derivatives as well as other low temperature solutions. Japan particularly has focussed on this area, since in any case their more eco-efficient soldering equipment allows lower temperature operations.

There are significant technical issues to be overcome, notably the oxidative instability of SnZn both as a solder paste and at joint interfaces. A stable flux is required, but these are likely to be a proprietary technologies rather than amenable to collaborative research.

Many solutions have been devised to overcome these issues for SnZn, notably addition of other elements. There is strong research and commercial interest in Europe to look at this topic more.

Some SnZn solder has been in commercial use in Japan for some years.

However, it appears that both solder manufacturers and CEM's are extremely reluctant in fact to take this route. Claimed benefits in material cost are small compared to the costs now known to be associated with qualifying a new solder alloy for use. Further the benefits of lower temperature are diminishing as materials and equipment is redesigned to adapt to higher lead-free temperature as industry standard.

There are also lingering sustainability doubts in Europe about using Bi, even if the Bi-lead compatibility issue does eventually become redundant.

An entirely different new approach explores the concept that use of nanoscale solder paste particles can be used to decrease melting point. This is discussed further below.

### **High Temperature Solders**

High lead, high temperature solders used inside components for applications such as die attach have been specifically exempted from the RoHS Directive since the consensus is that a cost-effective replacement doesn't exist.

SnAu can be used in some cases, but clearly is too expensive for widespread use in, for example, MEMS capping.

This has not been for lack of trying, and several potential solutions have been explored. The <u>Innolot project</u> included such work.

Efforts continue and important new initiatives are underway in Europe and in Japan. The COST 531 consortium of more than 60 skilled European metallurgists has recently begun a <u>new COST project</u> to tackle the issue. The Japanese NEDO project is exploring a ZnSn option.

If this can be achieved then RoHS compliance will be simplified, since currently these products represent legal lead in an electronic assembly.

## 3. Lead-Free Finishes

Lead-free finishes existed before lead-free solders were introduced, mainly as advanced surface treatments for boards to give levelling or improve solderability. These were mainly NiAu, immersion Ag, immersion Sn or OSP. Some NiPd-based systems and Sn finishes were used in component finishes.

With the advent of lead-free soldering, lead-free finish technologies have been more widely applied to components and boards, displacing SnPb solderable finishes.

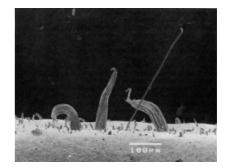

Whilst a number of finishes are in use for lead-free soldering, pure tin has emerged as a simple cost-effective solution for general use.

This has caused some alarm for those working with high-reliability products, particularly the US military and space sectors, where pure tin coatings had historically been prohibited on the basis of their propensity for developing tin whiskers leading to shorts. However, as detailed elsewhere, mitigation practices including thermal post-treatment of tin plated on copper provide sufficient protection against excessive whisker formation.

With several finish technologies alongside several lead-free solder technologies, the number of possible solder-finish combinations was large for compatibility studies. Very much of the early work in lead-free soldering technology was focussed on studying the effect of these combinations on solderability, joint strength, reliability etc.

In general, only Bi-containing systems emerged as having a potential

compatibility issue with SnPb or Pbcontaminated lead-free solders. Thus, although it is more widely used in Japan, Bi is not yet adopted in Europe as a finish component.

Although there is a call for a single solution it is likely that a number of finishes are likely to continue to be used for various technical and/or cost reasons.

There have been examples of technology developments in the field. OSP finishes have been advanced to give sufficient robustness for multi-pass performance in the higher temperature lead-free processing environment. New low-cost immersion Sn processes were developed in the <u>PRINT project</u>.

Future breakthrough technologies would be required for to eliminate the need for use of expensive precious metals by matching low-cost solutions with the high performance needed in some applications.

Much attention has been focussed on the lead-free solder-finish interface in regard to both tin whisker formation and intermetallic growth and properties. These are critical to reliability, and new failure mechanisms are still being discovered.

New technologies could focus on a paradigm shift by which it is the substrate itself that is changed or modified rather than addition of an expensive finish layer to standard copper/steel substrates.

Study of intermetallic growth for nanoscale joints will become critical, as diffusion and reaction dynamics have a greater influence. Already there are electromigration issues in small flip-chip bumps.

### 4. Substrates

#### **High Density Interconnection**

Technology trends, both at the board level and the component packaging level are beginning to converge. With the advent of 3D systems, printable electronics and embedded devices, the concept of the basic 'Printed Circuit Board' is already changing.

Modern substrates are already multilayer constructions with complex interconnection pathways and advanced composite technologies.

As components miniaturise, interconnection configurations evolve and patterning/construction techniques change this trend could continue, until potentially circuitry is fully embedded and the concept of a substrate disappears altogether.

In the meantime, new technologies are required to meet the challenges of HDI (High Density Interconnection), including new ways to decrease conductor width spacing and decreasing plating hole diameter, for example.

As density increases, so do issues of interference and thermal energy management. The advent of interconnections for RF and optical signals will add complexity.

There are also important implications of the trend towards high density for inspection, testing and reliability, discussed below.

Electrochemical migration failure effects clearly have a greater potential influence for higher density interconnections. The <u>HDPUG</u> (High Density Packaging User Group) has been focussing work for a number of years on these types of issues, including lead-free technology.

### **Thermal Degradation**

The increased process temperatures for lead-free soldering have thermally challenged most polymeric materials used in electronics assembly, as process temperatures approach degradation temperatures.

For the most part basic research in leadfree soldering was carried out with small to medium-sized boards, where thermal degradation problems were only seen with temperature sensitive components.

More recently, as the IT/telecoms and aerospace/defence industries have been drawn into the transition, larger and more complex boards have been shown to have serious problems. The iNEMI group identified major issues with substrate warping and delamination and with repair and rework.

Substrate technologies have indeed advanced to meet the challenge and new 'lead-free compatible' products are now available. However, it is now clear that factors such as interlayer moisture, channelling and via density, for example, can play an important part and that it is not just a matter of good epoxy materials.

Recent work at IVF, Sweden and elsewhere has shown new evidence of wide performance variation in round-robin tests of substrates with delamination, warping and poor CAF results.

### 5. Halogen-Free Materials

The halogens bromine and chlorine are commonly incorporated into polymers used in electronics, either additively or as a part of the polymer structure itself. Such polymers are used in PCB substrates, component packaging, wiring, connectors, and casings as fire retardants.

Halogen-containing products have been under pressure for some time, with even PVC being targeted by environmentalists. The RoHS Directive specifically bans two types PBB's and PDBE's. However, whilst there is a general drive towards halogenfree polymers, the particular situation is made complex by the large number of different polymers and applications. Enforcement of legislation is also hampered by the difficulties in speciating to differentiate between legal and illegal substances.

The ~30,000 tpa. brominated fire retardants used in Europe is divided roughly equally between TBBPA, HBCD and Deca-DBE.

Deca-BDE is used mainly in housings, connectors, switches and capacitors. Although theoretically exempted under the RoHS Directive, a recent ruling by the EU Commission has effectively banned its use by implicating a Nona-BDE impurity. This issue is still mired in controversy but could have a very significant impact in development of new technologies in the short-term.

Halogen-free technologies for substrates include alumina trihydrate (ATH) and other inorganic fillers, red phosphorus and organophosphorus/organonitrogen compounds, but all of these have associated issues, including, for example, problems with mechanical and/or electrical failures.

Problems with stability in the z-axis and optimisation of µvias in terms of interface performance have also been observed.

Across the board the alternatives are more expensive than bromine. Also there is the doubt that phosphorus systems are indeed more environmentally acceptable than bromine.

There are a number of technologies that may be capable of cost-effectively replacing bromine, using nanocomposites with ZnSn or nanoclays, for example.

However, whilst it is still possible to use legal substances, industry will be reluctant to accept the costs of pursuing development and qualification of alternative technologies.

### 6. Underfills & Encapsulants

Underfill technologies are being adopted more widely. They are used to improve reliability for sensitive components under increased mechanical strains or for potting inside components.

Their use is also coupled with the increase in adoption of bare die technologies and this can be developed further.

However, their use is restricted by inability to carry out rework on the component should it become necessary. Technological progress may thus be focussed on underfill products that are reworkable, without land damage.

Other challenges include development of more user-friendly approaches, for example in a one-step application before reflow, or adoption of quick or no-cure systems.

The topic of conformal coatings is under review in Europe, led by <u>NPL, UK</u>. Preliminary work has shown that current coatings may be more permeable to dibasic acids from fluxes than previously thought, and that surface contamination plays an important role.

Industry feedback suggests that although there is a conservative attitude by some, others are anxious to fundamentally reassess conformal coatings technologies and develop new solutions.

The need for a wider industry consultation is indicated, with a common agreement on performance-led standards.

New technologies will need to consider a wide range of needs as well as basic barrier performance. These include eco-friendliness, the ability to deal with

ELFNET Roadmap – Electronics Interconnection Research Version 1 – October 2006

contaminant residues without requiring a cleaning step and the ability to rework/repair coatings on a localised basis.

## 7. CTE Matching

The new thermal issues generated by the introduction of lead-free solder processing has had and will continue to have a wide ranging impact on materials selection for electronics assemblies, particularly in high reliability products.

Further there is an increased focus on thermal issues in use, notably in harsh environments, for example automotive application. This is exacerbated by the greater localised heat generated in use by miniaturisation and greater integration.

The component mix is also becoming more complex, with a consequent introduction of more materials technologies and plurality of interconnection technologies. Optical PCB's are an example of the new challenges ahead.

The use of CTE (Coefficient of Thermal Expansion) matching brings a more thermally intelligent approach to assembly design, being in general the use of better thermal management techniques during processing and use.

These can be physical or structural technologies. An example of this would be the <u>Alpha CoolCap</u>, designed to shield temperature sensitive components during rework. In theory these types of techniques can minimise expansion of high CTE materials but in practice the board assembly is so complex that other parts of the board design may be adversely affected, for example.

Heat dissipation using conductive materials and channels may become more important.

Alternatively this could involve development and use of materials based on achieving CTE compatibility for adjacent materials to eliminate strain under temperature excursions.

A successful approach has been to design CTE-matched interposer layers of copper or other materials between die and substrate, for example.

The use of such interposers or 'transposers' can be effective, but again the knock-on effects on the whole board processing have to be accounted for.

FEM modelling can be used to assist in design, but in practice models are not particularly adequate and intuition is used with success just as often.

CTE acts in 3 dimensions although it is the xy of board plane, where the greatest challenges lie. Mismatch in the perpendicular z plane is crucial to reliability of vias.

Ceramics have a low CTE and high insulation and are used in high value high temperature applications. They are however expensive. Technological advances should include shrinkage control using predictive modelling and feature minimisation, with cost-effective higher quality products.

Via integrity during lead-free processing has been the subject of recent studies. It is possible, though challenging, to envisage the development of alternative via materials using polymers, other metals or ductile materials.